Einstieg Takt

Zeitliche Abläufe

Das RS-Flip-Flopändert seinen Zustand und damit seine Ausgänge "Q" und "Q nicht" nicht, wenn

r = s = 0 ist, also weder gespeichert noch rückgesetzt werden soll. Dann bleiben die Ausgänge wie zuvor, also Q neu = Q alt. Um von einem "neuen" und "alten"

Ausgang sprechen zu können, ist eine Art Zeitgeber notwendig, also eine neutrale oder höhere Instanz, welche festlegt,

wann der neue Zeitpunkt gekommen ist

und damit ein bis dato aktueller oder neuer Ausgang Q zu einem alten Ausgang Q alt wird.

Man kann dies mit unserer Zeit vergleichen: Aktuell, also genau jetzt, gibt es eine (neue) Uhrzeit t oder t neu. Die Uhrzeit vor einer Minute, sagen wir t - 1,

ist also eine vergangene, alte Uhrzeit.

Könnten wir die Zeit zurückstellen und die aktuelle Uhrzeit wäre t - 1, so wäre z.B. t - 2 (also wieder eine Minute in die Vergangenheit), die alte Uhrzeit

„t alt" und t - 1 die neue, aktuelle „t neu".

Aufgabe 1

Teste und beschreibe den Baustein Clock mit Hilfe der nachfolgenden Schaltung. Klicke dazu rechts auf den Schalter. Klicke auch auf die „1“

in dem Baustein. Drücke die Backspace-Taste (deutsch: Rücktaste oder Rücklöschtaste über der Eingabe-Taste) oder Entferne-Taste („Entf"), ändere den Zahlenwert (positive, ganze Zahlen)

und drücke die Eingabe-Taste. Erkläre deine Beobachtungen.

Alternativ kannst du dir auch die

Dateifür die Simulationssoftware LogicSim herunterladen. Mit Rechtsklick auf den Baustein, Eigenschaften kannst du auch hier

Einstellungen vornehmen. Teste diese und vergleiche mit den Ergebnissen aus der nachfolgenden Schaltung!

Aufgabe 2

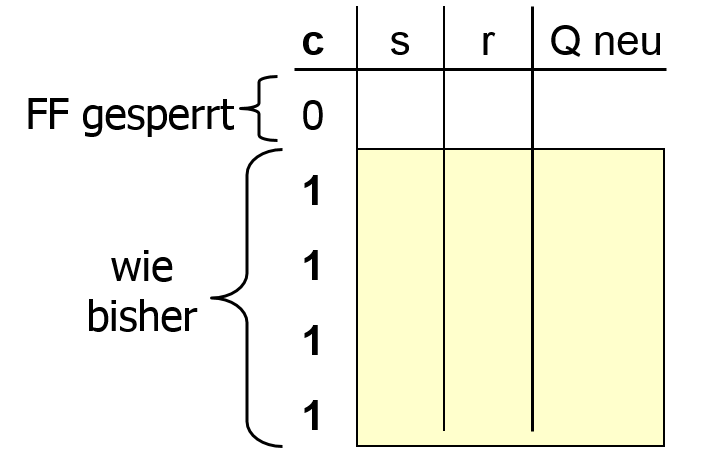

In dieser Aufgabe geht es nun darum, mit Hilfe eines Zeitgebers c (engl. Clock) ein RS-Flip-Flop zu steuern:

(a) Vervollständige die nachfolgende Schalttabelle:

(b) Ergänze dein RS-FF um einen weiteren Eingang, sodass nur, wenn der Takt c den Wert 1 hat, ein Setzen oder Rücksetzen des Flip-Flops erfolgen kann.

Idee: Ein Tor steuert, ob s und r „durchgelassen“ werden. Nutze dazu ein Grundgatter.

Tore werden mit AND-Gattern gesetzt, denn nur, wenn beide Eingänge logisch auf high (1) stehen, wird der Ausgang auch high (1).

Quellen

- [1]: - Urheber: SD - Lizenz: inf-schule.de